基本概念

1. 建立时间

是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

2. 保持时间

是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

3. 时间裕量

建立时间裕量:Tsetup_slack

就是说在满足建立时间的情况下,所剩余的时间长度为多少,一般大于0;

保持时间裕量:Thold_slack

就是说在满足保持时间的情况下,所剩余的时间长度为多少,一般大于0;

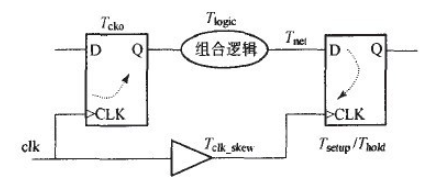

4. 组合逻辑电路延迟 Tlogic

两级触发器之间的组合逻辑电路会给信号带来延迟,这个时间就是Tlogic

5. Tco

表示触发器输入端D到输出端Q的延时

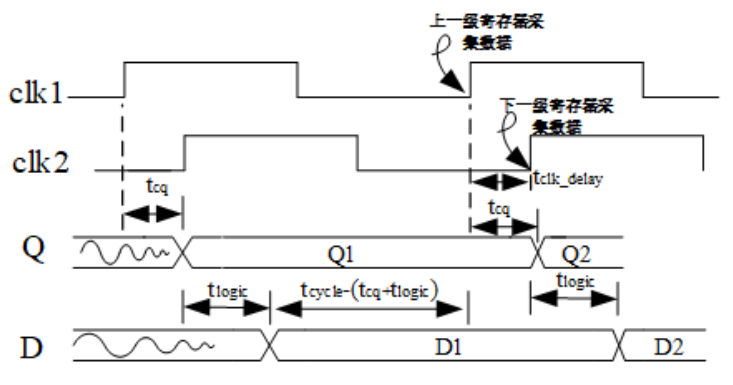

下图是触发器时序电路图以及建立时间裕量和保持时间裕量计算公式:

时序分析

理想情况下的建立时间最大值(就是目的寄存器时钟上升沿的时候,上一数据刚要结束,就被采集到了,也就是数据建立的太早了,数据建立时间出现最大值,保持时间为0),

理想情况下的保持时间最大值(目的寄存器时钟上升沿的时候,数据刚开始,被采集到了,也就是数据建立的太晚了,出现建立时间0,数据保持时间出现最大值)。

但是实际情况下,寄存器没有这么灵敏,结果就是电路不稳定,出现亚稳态现象。

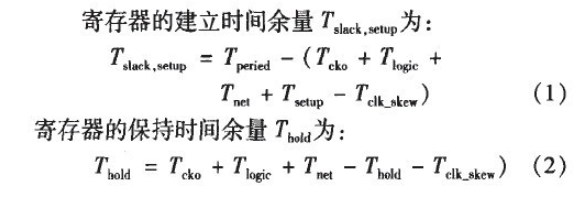

1. 建立时间裕量

如下图。展示的是D1触发器输出端Q的波形和D2触发器输入端D的波形

有图可见。D2触发器输入端数据D提前于clk上升沿的时间为 tcycle-(tco+tlogic),那么他就有这么长的时间来满足建立时间的要求,如果要满足建立时间的话,就要Tcycle-(Tco+Tlogic) > Tsetup,

即Tsetup_slack = Tcycle-(Tco+Tlogic) - Tsetup > 0 ,如果加上时钟偏移Tclockdelay,就是Tcycle-(Tco+Tlogic) + Tclockdelay > Tsetup,

即Tsetup_slack = Tcycle-(Tco+Tlogic) - Tsetup + Tclockdelay > 0,如下图

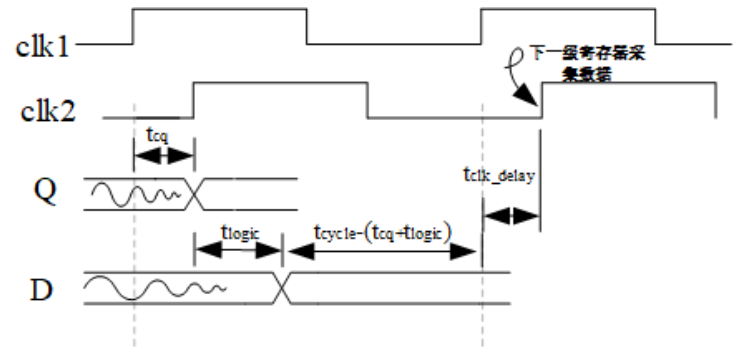

2. 保持时间裕量

如下图,展示的是D1触发器输出端Q的波形和D2触发器输入端D的波形

有图可见。D2触发器输入端数据D在clk上升沿到达后的可以持续时间为 Tco+Tlogic。如果要满足建立时间的话,就要Tco+Tlogic > Thold,

即Thold_slack = Tco+Tlogic - Thold > 0 ,如果加上时钟偏移Tclockdelay,就是Tco+Tlogic-Tclockdelay > Thold,

即Tco+Tlogic-Tclockdelay-Thold > 0,如下图

PS:图片来自网络