在前面时序约束入门(一),我们了解了时序约束的一些基本概念,包括建立时间裕量、保持时间裕量等,现在我们具体来了解在fpga上如何实现时序的约束。

本文主要以vivado为例。

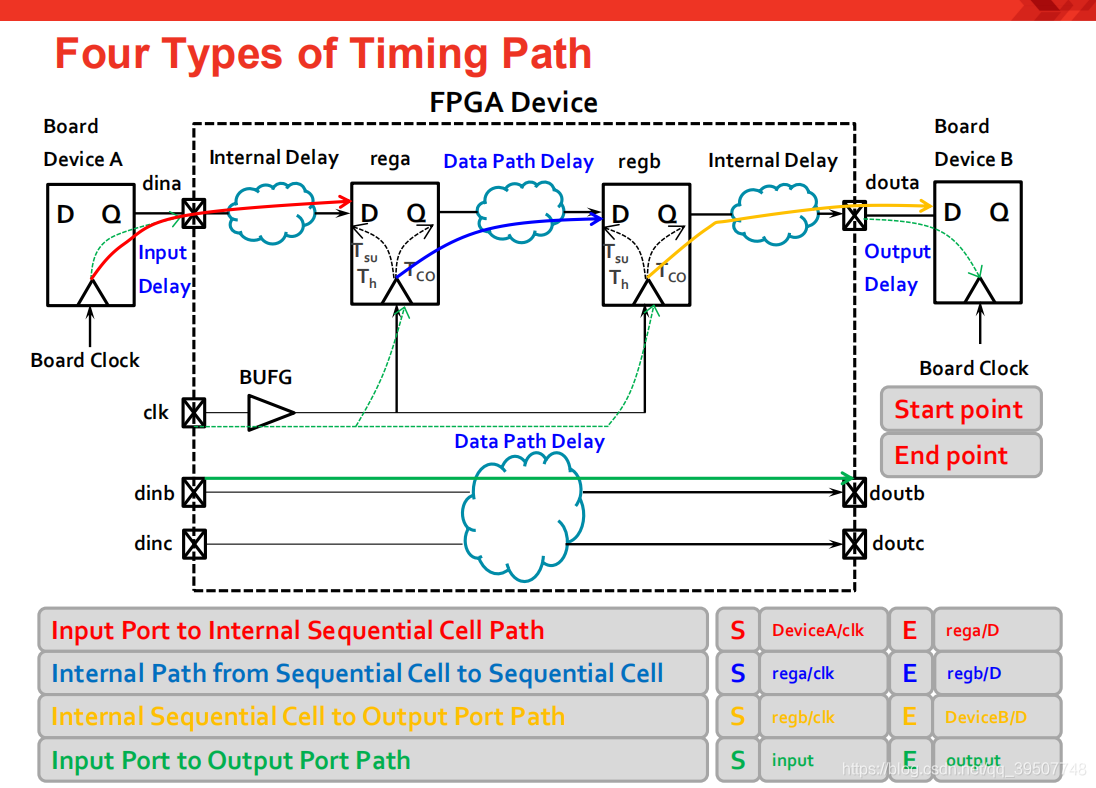

不同路径约束方法不一样,

| 路径 | 约束方法 |

|---|---|

| 模块内部触发器之间路径 | create_clock |

| 上一模块寄存器输出到本模块寄存器输入 | set_input_delay |

| 本模块寄存器输出到下一模块寄存器输入 | set_output_delay |

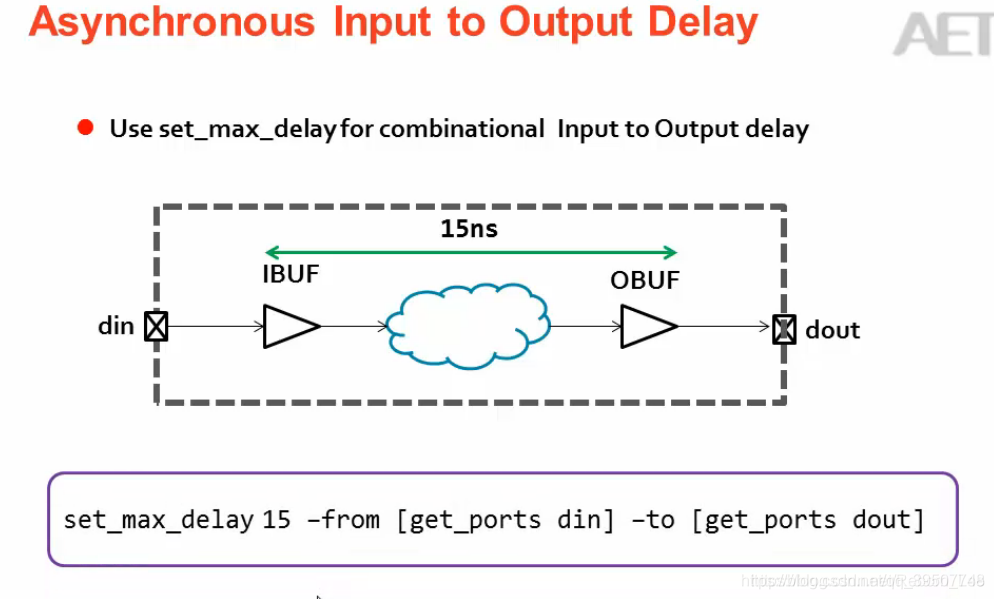

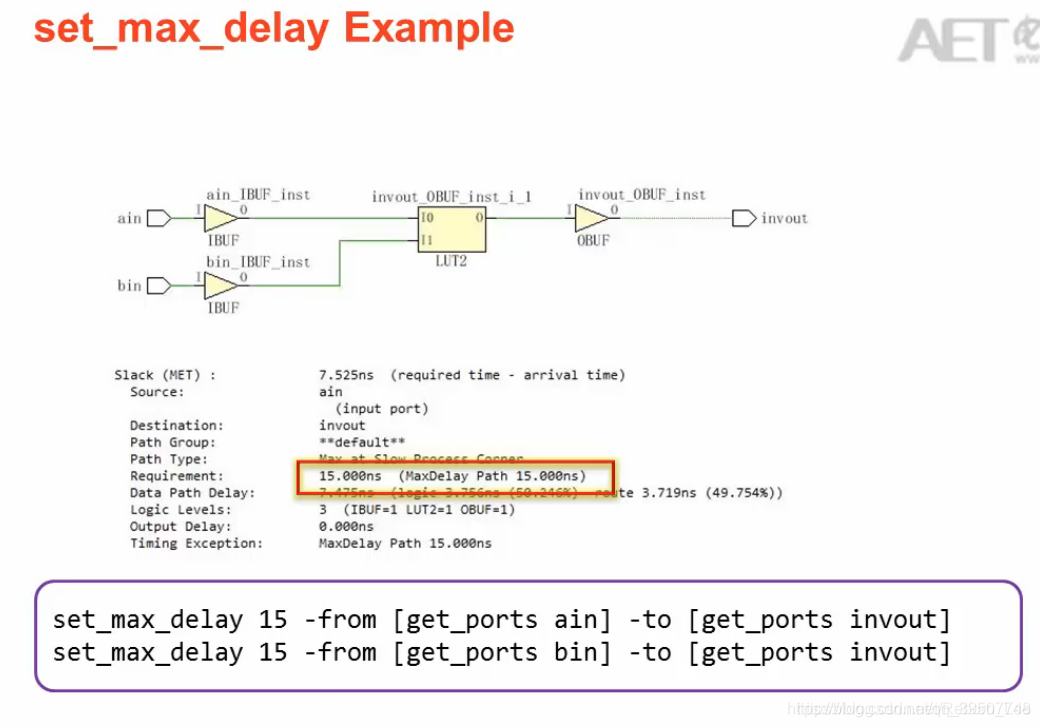

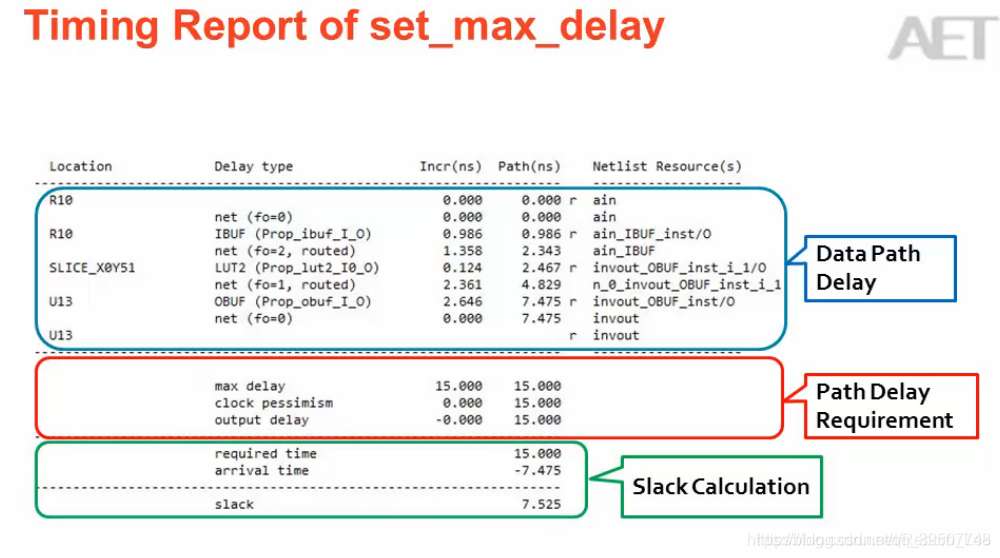

| 本模块输入口到输出口 | set_max_delay |

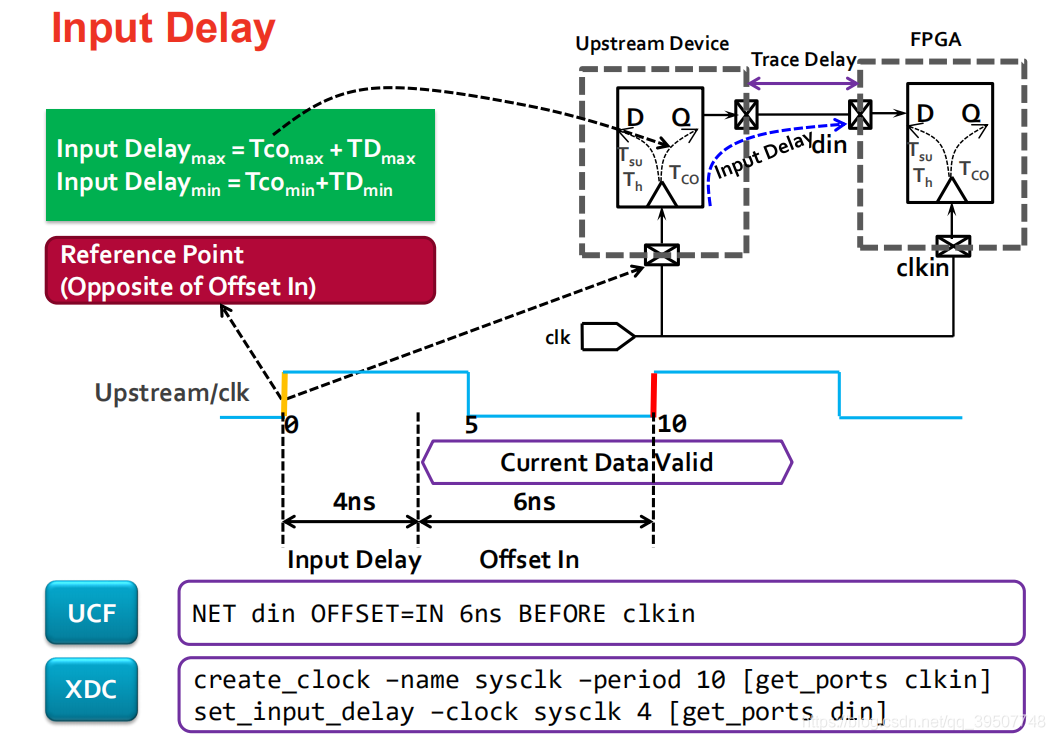

输入延时

由下图可以看出Input Delay是以上游芯片的时钟发送沿为参考,上游的时钟端到达本模块外部输入端口之间的时间差。

输入延迟(input delay)包括Tco和Trace Delay(板间延迟),其中Trace delay又叫Board delay。

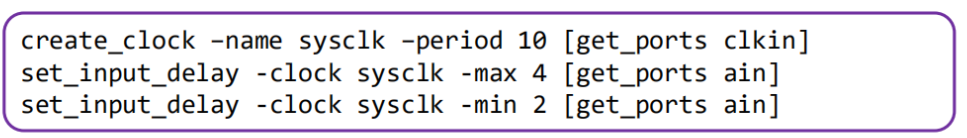

约束的写法为:

如果同时设置了max和min delay,那么max值是用在对Input Setup Timing的分析中的,而min值用在对Input hold Timing的分析中。如果只设置了一个值,那么同时供两者使用!!!

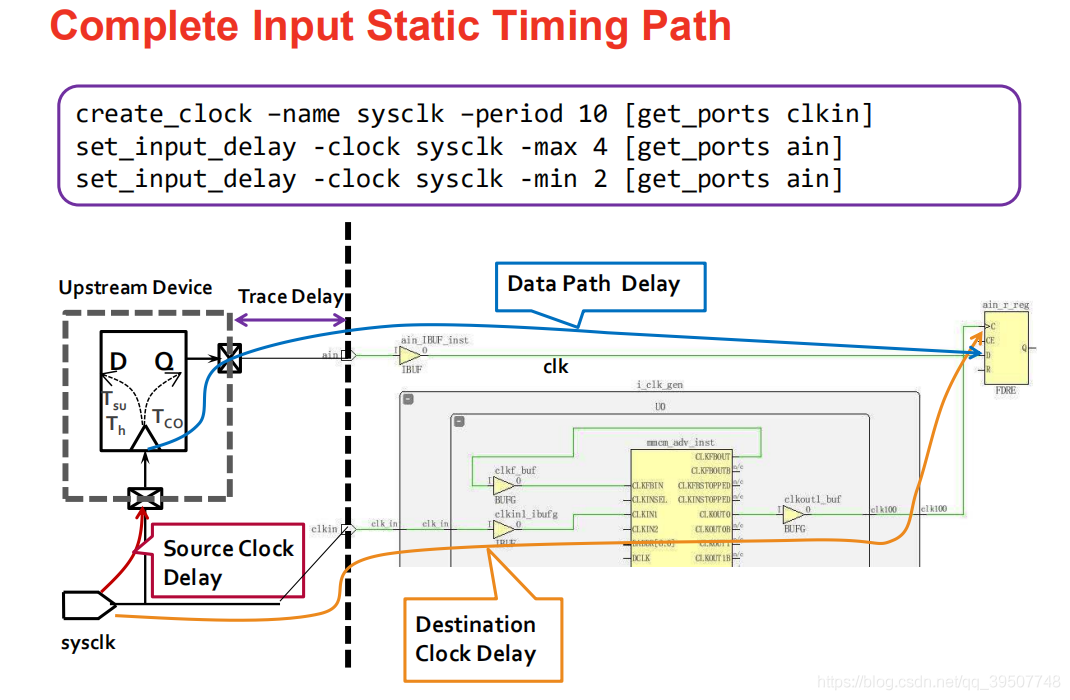

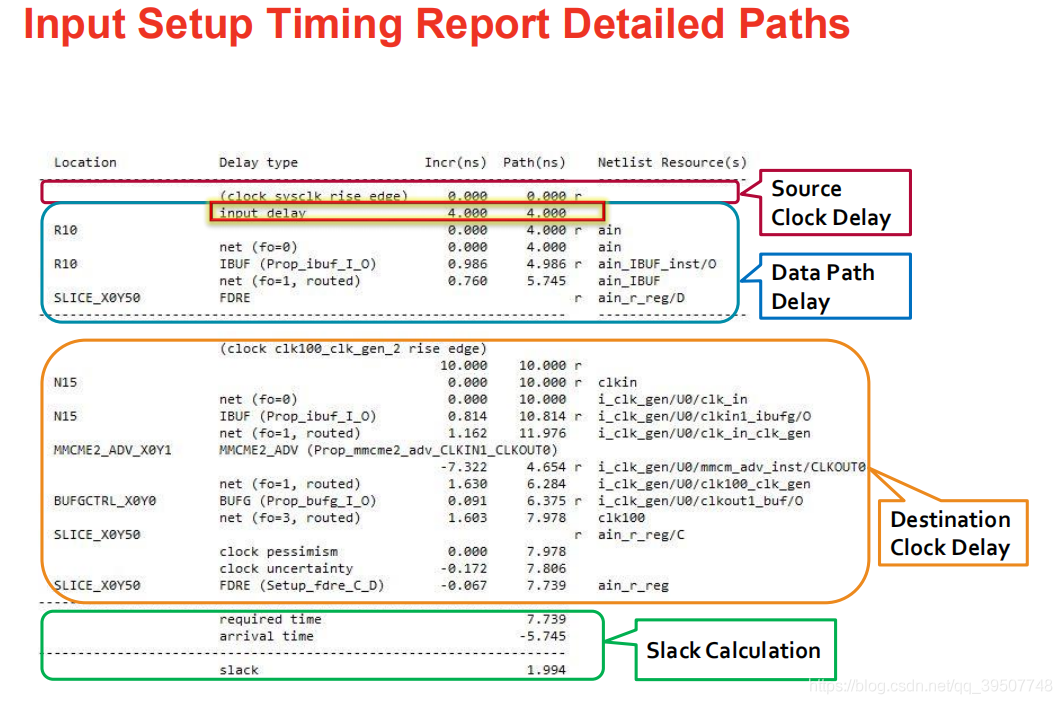

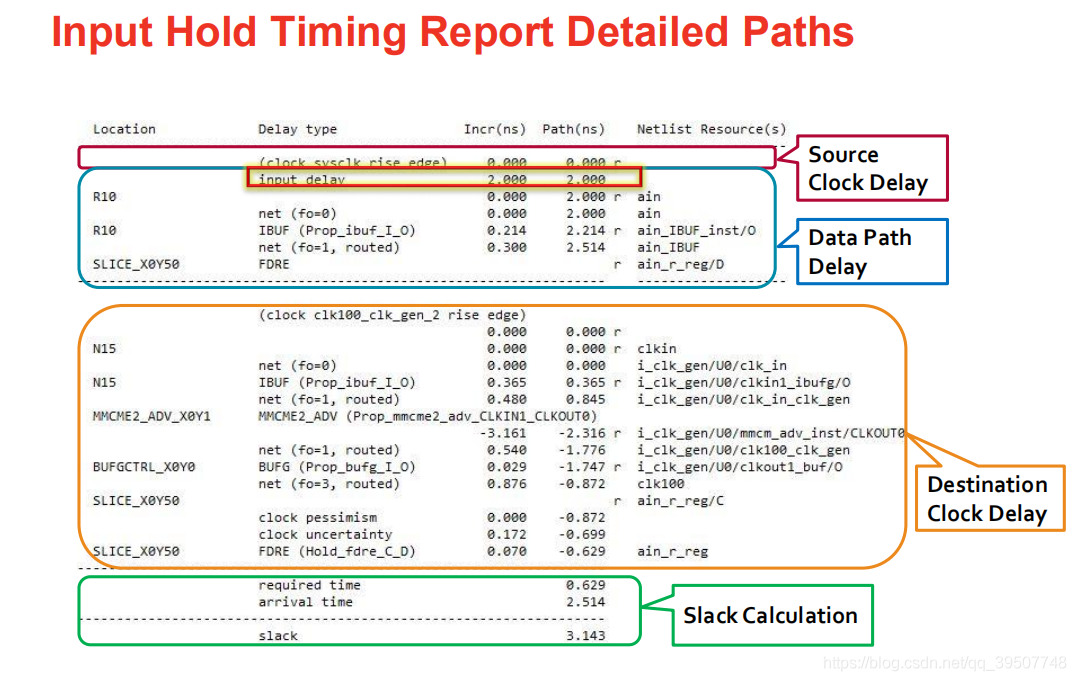

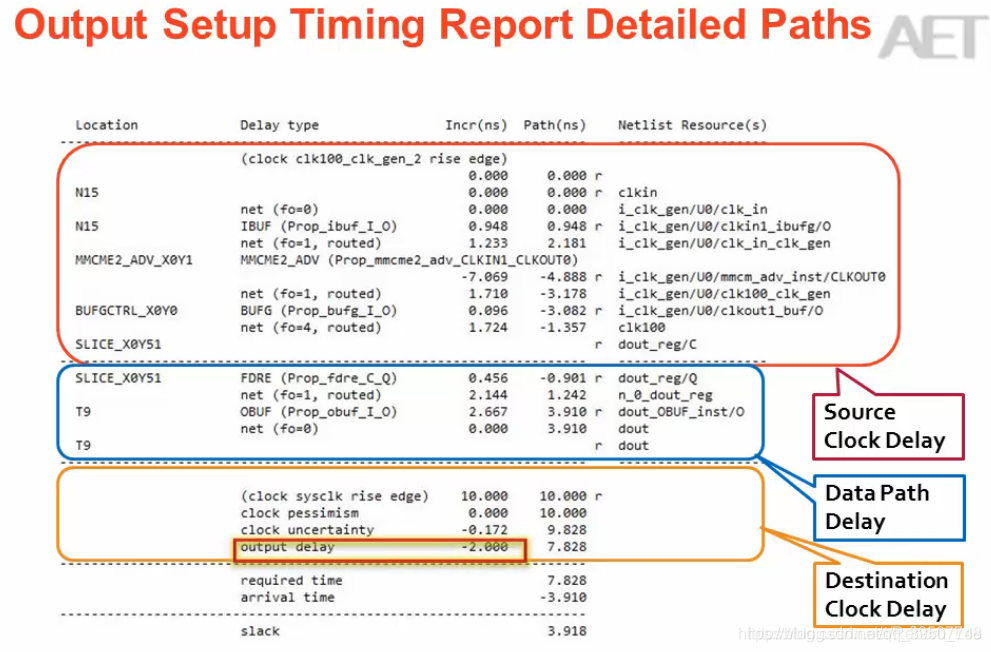

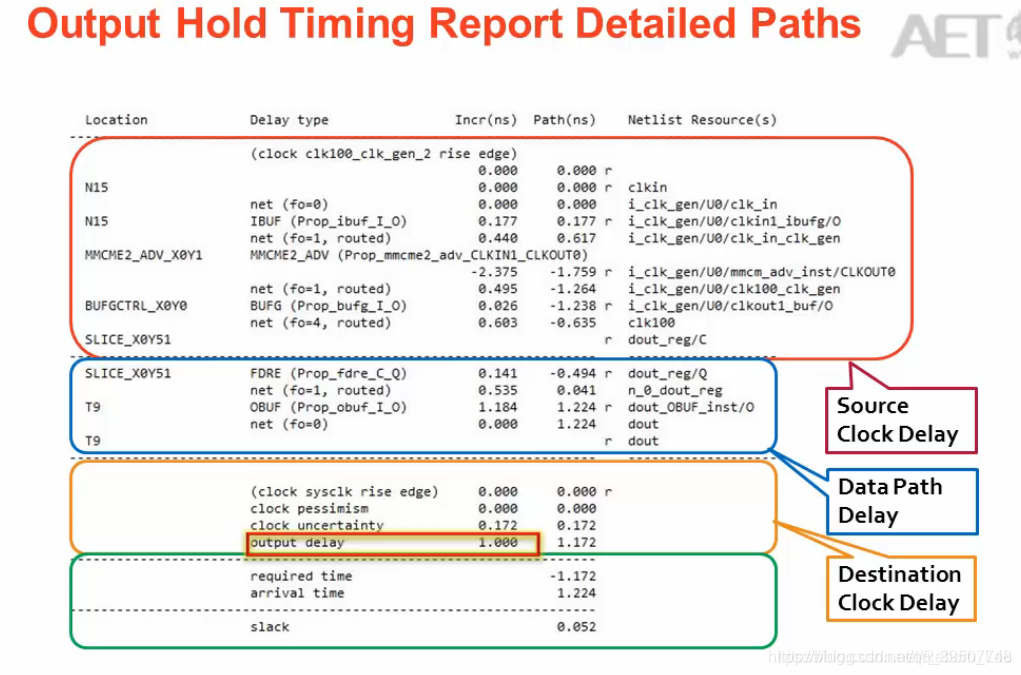

约束能够让软件优化布线布局,同时时序分析报告把时序路径分为三部分,然后分别计算各部分的延时,最后计算出裕量slack,根据slack的值来判断时序是否正确。

source clock path + data path = 实际的数据到达延迟路径;

T(destination clock path) - Ts(或者+Th) = 数据需求时间;

在计算数据需求时间时,如果是对建立时间进行时序分析,那么在T(destination clock path) - Ts中,destination clock path的初始时间就是一个clock周期;

而在对保持时间进行时序分析的时候,在T(destination clock path) +Th中,destination clock path的初始时间为0

输入延时建立时间分析报告:

输入延时保持时间分析报告:

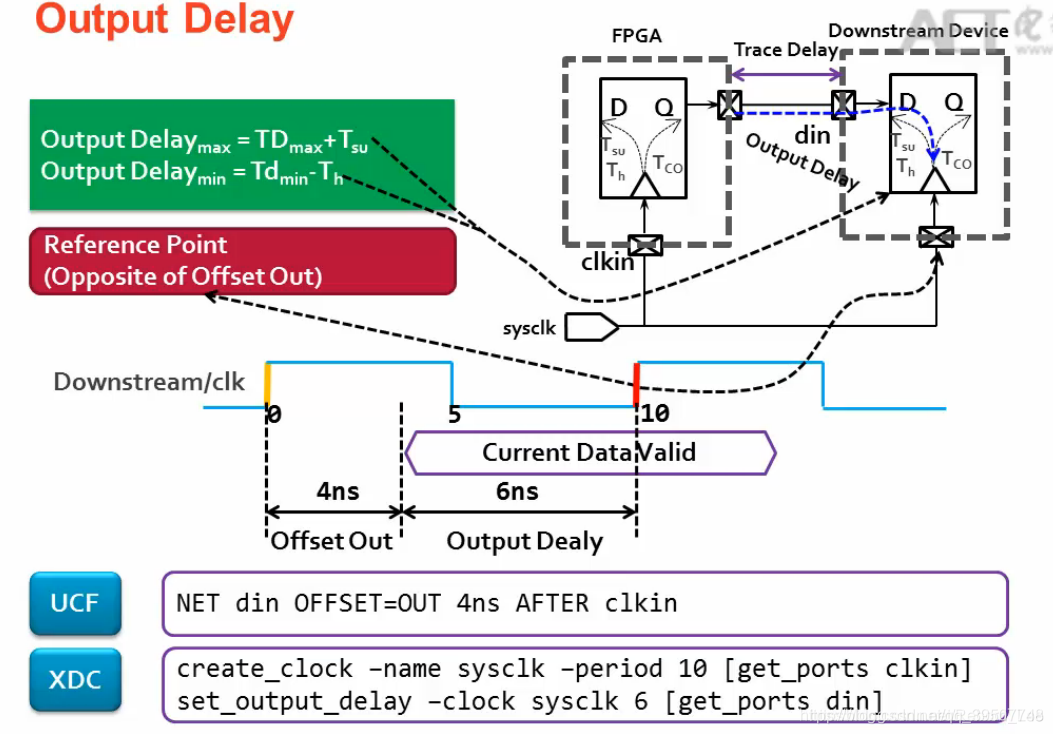

输出延时

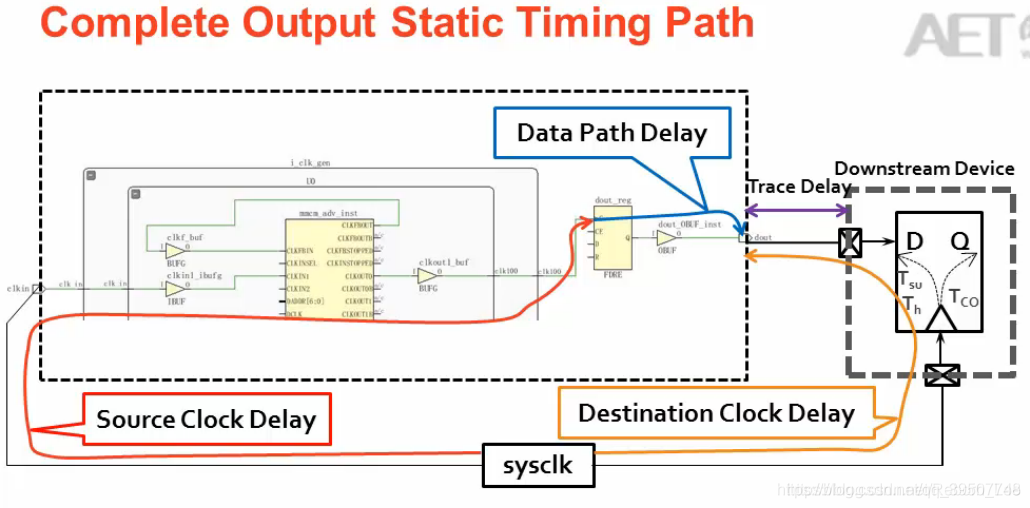

output delay以下游芯片时钟端为参考。本模块输出端数据到达下游时钟端的时间差。

输出延迟(output delay)包括Tsu和Trace Delay(板间延迟)。

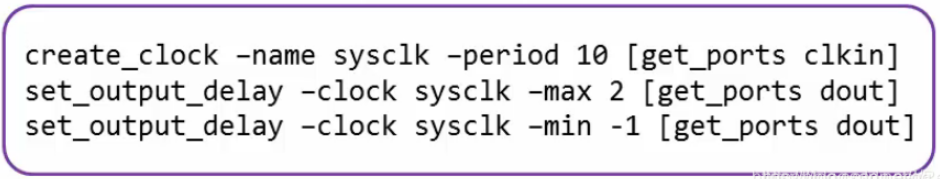

约束的写法为:

输出路径分析可以分成这三部分

输出延时建立时间分析报告:

输出延时保持时间分析报告:

最大延时

组合逻辑电路输入到输出的延时

最大延时约束举例:

最大延时约束分析报告: