CMOS电路中的功耗分为两部分:静态功耗和动态功耗;

静态功耗是由漏电流引起的功耗;动态功耗分为翻转功耗和短路功耗,翻转功耗也就是0与1翻转所引发的功耗,而短路功耗则是由于PMOS和NMOS都导通时所引起的功耗;

我们可以在五个层次下对系统的功耗进行优化,自顶向下分别对应系统级、行为级、RTL级、逻辑级和物理级;

对于前端设计人员,我们要熟悉在RTL级对电路进行低功耗优化。

并行与流水处理

采用并行处理,可以降低系统工作频率,从而可能降低功耗。

流水线技术可以将一个较长的组合路径分成M级流水线。路径长度缩短为原始路径长度的1/M。 这样,一个时钟周期内充/放电电容变为C/M。如果在加入流水线之后,时钟速度不变,则在一个周期内,只需要对C/M进行充/放电,而不是原来对C进行充/放电。因此,在相同的速度要求下,可以采用较低的电源电压来驱动系统。这样,系统的整体功耗可能会降低。

资源共享

在多算数运算的代码里,我们可以资源共享,例如:

assign sum1 = a + b +c +d;

assign sum2 = a+c+e;

assign sum3 = d +b+e;可以改成

assign sumac = a+c;

assign sumbd = b+d;

assign sum1 = sumac+sumbd;

assign sum2 = sumac +e;

assign sum3= sumbd + e;前者用了七个加法器,后者只用了五个,少用了资源自然也就降低了功耗。

编码

正常二进制编码每一次变化都要多位翻转,如果转换成格雷码,相邻两数变化只会翻转一位,功耗也降低了。

操作数隔离

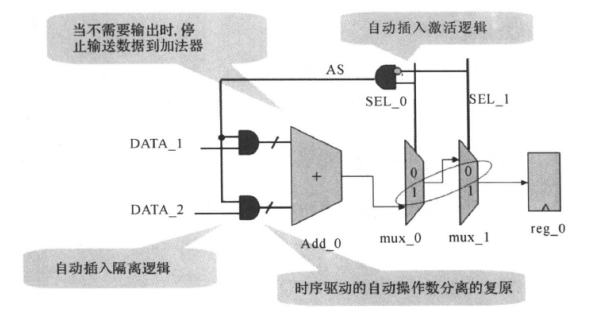

操作数隔离的原理就是:如果在某一段时间内,数据通路的输出是无用的,则将它的输入置成个固定值,这样,数据通路部分没有翻转,功耗就会降低。

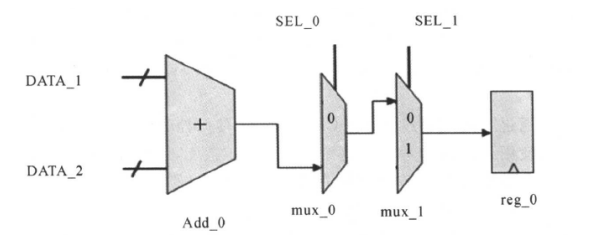

如图:

上面的电路图中,当SEL_0≠1,SEL_1≠0时,加法器Add_0的运算结果并不能通过mux_0和mux_1到达寄存器reg_0的输入端口,也就是说寄存器reg_0将不会保存加法器Add_0的运算结果,这就意味着加法器Add_0的运算是不必要的。为了节省功耗,我们可以用操作数分离的方法,在某些条件下,使加法器不工作,保持静态,进行操作隔离之后的电路如下所示:

门控时钟

芯片功耗组成中,有高达40%甚至更多是由时钟树消耗掉的。那么减少时钟网络的功耗消耗,最直接的办法就是如果不需要时钟的时候,就把时钟关掉。

门控时钟大概有这么几种:

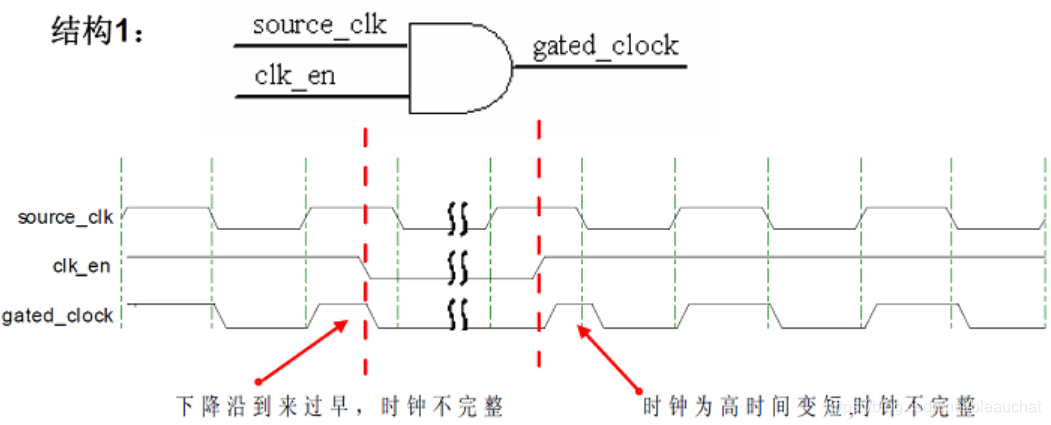

1、与门门控

我们只需要把enable和CLK进行“与”操作。

这种直接将控制EN信号和时钟CLK进行与操作完成门控的方式,可以完成EN为0时,时钟被关掉。

但是同时带来另外一个很大的问题:毛刺。EN是不受控制的,随时可能跳变,这样纯组合输出GCLK就完全可能会有毛刺产生。

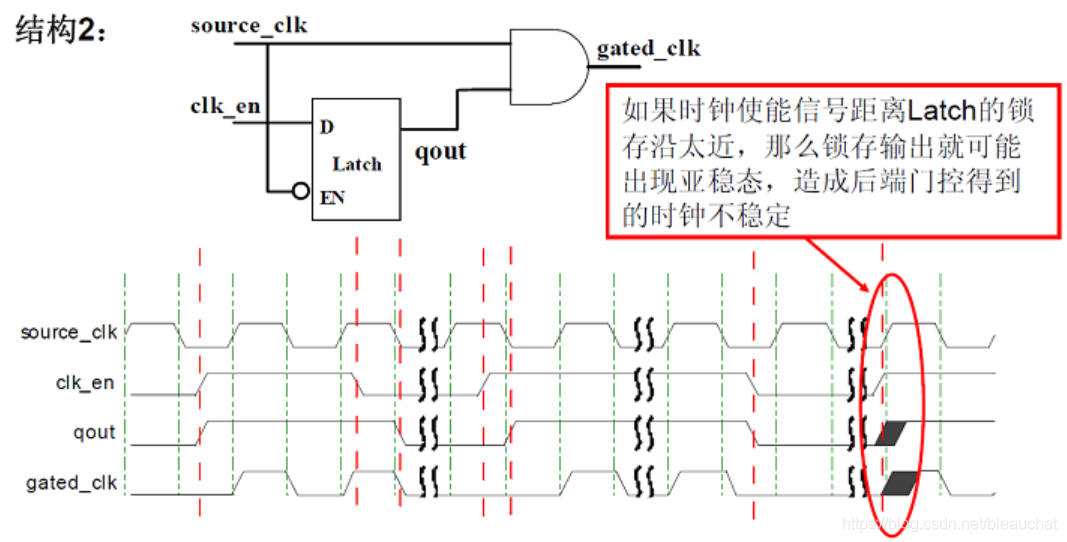

2、锁存门控

只有在CLK为高的时候,GCLK才可能会输出高,这样就能消除EN带来的毛刺。这是因为D锁存器是电平触发,在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。

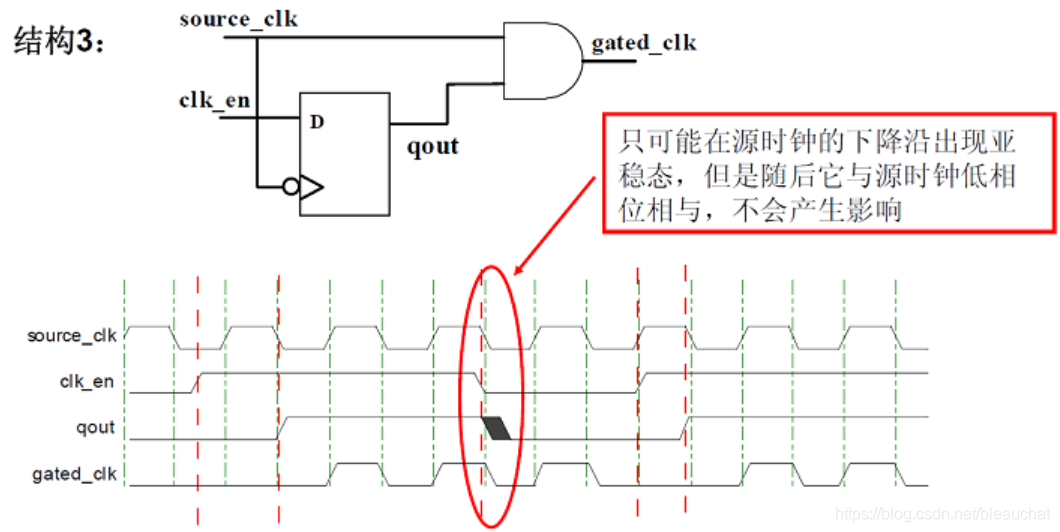

3、寄存门控

用寄存器来寄存EN信号再与上CLK得到GCLK,

SOC芯片设计中使用最多的是锁存结构的门控时钟。那么RTL中怎么才能实现门控时钟呢?答案是不用实现。现在的综合工具比如DC会自动插入门控时钟。

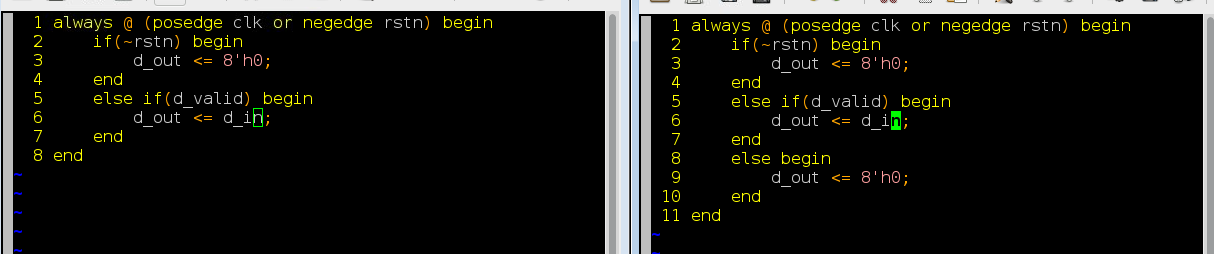

但综合工具自动插入门控时钟也是有一定条件的。

左边可以综合出门控时钟,右边的不可以。

所以在不用的时候把数据设成0并不能减少功耗,保持数据不变化才能减少翻转,降低功耗!

参考资料:https://blog.csdn.net/l471094842/article/details/103631370