AXI4-stream接口连接产生数据的一个主设备和接收数据的一个从设备,用来传播数据流,和其他AXI协议不同的是,AXI4-stream不需要主机提供地址,使用相对方便,当传输单数据时其数据传输时序与第一讲的APB总线就少了个地址信息的,其他大致相同。

接口信号

ACLK: 系统时钟

ARESTEN: 复位信号,低电平有效

TVALID: 表示主机正在进行数据传输

TREADY: 表示从机已经做好数据接收的准备

TDATA: 传输的数据

TSTRB: 字节控制信号,按照byte指定data中的哪个byte是地址信息或者数据信息;

TKEEP: 字节控制信号,指定data中的哪个byte是字节修饰符,哪个是有效的。

TLAST: 表示数据流的最后标志

TID: 标识符,表示不同数据流

TDEST: 提供路由信息

TUSER: 用户自定义信息

PS:如果TKEEP引脚不在的话,TSTRB承担指定字节有效的功能

数据传输

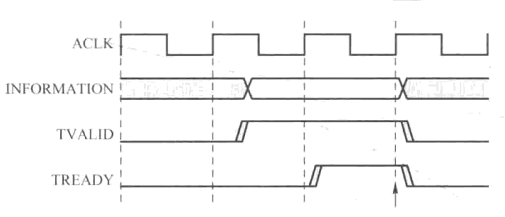

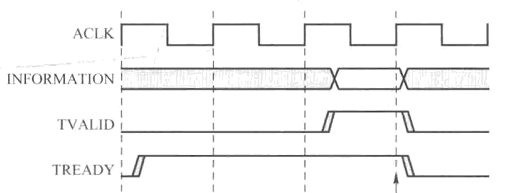

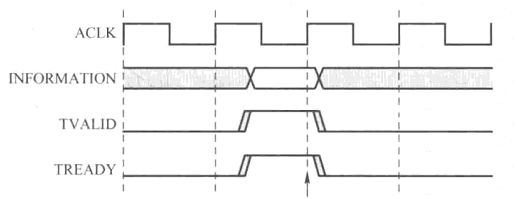

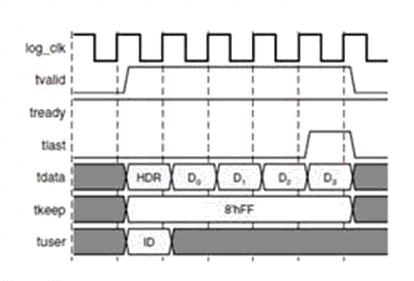

首先主设备给出数据和控制信息,并拉高TVALID信号,然后等待从机的TREADY信号,一旦TREADY信号为高,数据就开始传输,一般来说,无论TVALID和TREADY谁先到达,只有当TVALID和TREADY信号同时为高时,一次传输才算完成。如果连续多包数据传输的话,TVALID将一直拉高,直到最后一包数据传输,TLAST拉高。传输完成后,TVALID拉低,TLAST拉低。

直接放图会更容易理解。以下为TVALID和TREADY握手示意图:

多次连续传输示意图,

修改自定义AXI4-stream ip核

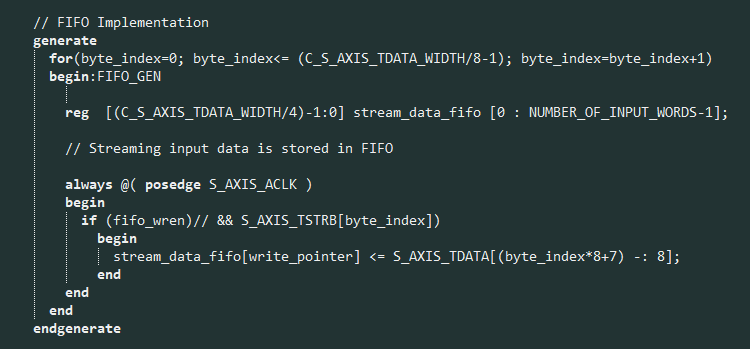

官方生成的带有AXI4-stream接口的IP核,是用一个二维数组来存放stream——data,但这不方便读出来进行二次开发,于是我做了一点改动,官方源码部分截图如下

笔者修改后的源码部分:

reg [0 : NUMBER_OF_INPUT_WORDS-1] [C_S_AXIS_TDATA_WIDTH-1:0] data_fifo ;

// FIFO Implementation

generate

for(byte_index=0; byte_index<= (C_S_AXIS_TDATA_WIDTH/8-1); byte_index=byte_index+1)

begin:FIFO_GEN

// reg [(C_S_AXIS_TDATA_WIDTH/4)-1:0] stream_data_fifo [0 : NUMBER_OF_INPUT_WORDS-1];

// Streaming input data is stored in FIFO

always @( posedge S_AXIS_ACLK )

begin

if (fifo_wren && S_AXIS_TSTRB[byte_index])

begin

data_fifo[write_pointer][(byte_index*8+7) -: 8] <= S_AXIS_TDATA[(byte_index*8+7) -: 8];

end

end

// always@(*) begin

// data_fifo[write_pointer][(byte_index*8+7) -: 8] = stream_data_fifo[write_pointer];

// end

endPS:图片来自网络