学完了AXI4-stream总线,我们继续来学习AXI4—lite总线。虽然同属于AXI4协议,但两者还存在较大差别。

AXI4-lite总线是AXI4总线的简化版,仅支持32位或64位数据读写,而且每次只支持一次数据的读写。即猝发长度为1。这一特性限制了它只能用于小数量的数据传输.

独立通道

AXI4-lite有五个独立的通道

读地址通道(Read address channel AR)

读数据通道(Read data channel R)

写地址通道(Write address channel AW)

写数据通道(Write data channel W)

写应答通道(Write response channel B)

每个通道都是双向握手机制通信,具体握手流程可参照前文axi4-stream总线所述,

那这几种通道如何配合工作完成一次完整的数据通信呢?

写数据过程:

首先主机发出写地址和控制信号,然后发出一次写数据,最后从机进行写应答。无论发送地址、数据、应答都是双方通过握手协议完成。

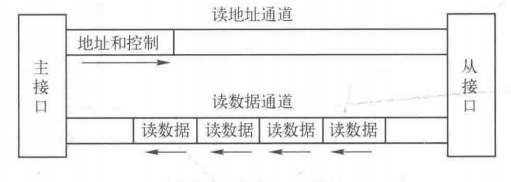

读数据过程:

首先主机发出读地址和控制信号,然后从机发送读数据。比起写数据过程,读数据过程少了一个应答环节。

信号线详解

全局信号

ACLK 全局时钟信号,在上升沿时对信号采样。所有的输入信号都通过上升沿采集,所有的输出信号都在上升沿时变化。

ARESETn 全局复位信号,低电平有效。在复位期间,所有的xxVALID信号必须复位为低电平。其他的信号可以是任意值。

写地址通道信号

主机(master)控制的信号

AWVALID

AWADDR 地址信号线,传输地址信息。

AWPROT 访问权限信号线,xilinx建议赋值为3’b000.xilinx IP 一般忽略此信号。

从机(slave)控制的信号

AWREADY

写数据通道信号

主机(master)控制的信号

WVALID

WDATA 数据信号线,传输数据信息。

WSTRB 数据总线有效字节控制。比如32位的总线,WSTRB等于4’b0010,那么代表WDATA[15:8]中的数据有效。其他无效。如果要求WDATA[31:0]32位全有效,那么WSTRB就应该等于4’b1111.

从机(slave)控制的信号

WREADY

写应答通道信号

主机(master)控制的信号

BREADY

从机(slave)控制的信号

BVALID

BRESP 应答类型。2bit信号

OKEY 00 正常访问成功

EXOKAY 01 独占访问成功,AXI4-lite不支持

SLVERR 10 从机错误,出现的原因有:FIFO 或者缓冲区溢出主机发起了不支持的传输位宽、尝试向读保护的地址写入数据、超时

DECERR 11 解码错误,比如没有从机的地址。

读地址通道信号

主机(master)控制的信号

ARVALID

ARADDR 地址信号线,传输地址信息。

ARPROT 访问权限信号线,xilinx建议赋值为3’b000.xilinx IP 一般忽略此信号。

从机(slave)控制的信号

ARREADY

读数据通道信号

从机(slave)控制的信号

RREADY

主机(master)控制的信号

RVALID

RDATA 数据信号线,传输数据信息。

RRESP 同写应答信号BRESP